Pour contrecarrer le mouvement des processeurs graphiques (GPU) dans le domaine du calcul scientifique de haute performance (HPC), Intel a lancé en 2013 ses coprocesseurs Xeon Phi. Lidée principale est de fournir un grand nombre de curs (une soixantaine pour la première génération), atout principal des GPU (les modèles actuels montent à plusieurs milliers de curs). La première génération de Xeon Phi est notamment utilisée dans le supercalculateur chinois Tianhe-2, le plus puissant au monde depuis sa construction en 2013, selon le classement Top500.

Pour contrecarrer le mouvement des processeurs graphiques (GPU) dans le domaine du calcul scientifique de haute performance (HPC), Intel a lancé en 2013 ses coprocesseurs Xeon Phi. Lidée principale est de fournir un grand nombre de curs (une soixantaine pour la première génération), atout principal des GPU (les modèles actuels montent à plusieurs milliers de curs). La première génération de Xeon Phi est notamment utilisée dans le supercalculateur chinois Tianhe-2, le plus puissant au monde depuis sa construction en 2013, selon le classement Top500.Cependant, comme pour les GPU, ces curs sont très différents de ceux des processeurs plus traditionnels (comme les gammes Core i3-7 dIntel, par exemple) : ils sont nettement moins véloces, avec des fréquences de lordre du gigahertz le parallélisme de ces coprocesseurs est leur principale caractéristique. Néanmoins, contrairement aux GPU, ils peuvent se programmer dune manière très similaire aux processeurs classiques.

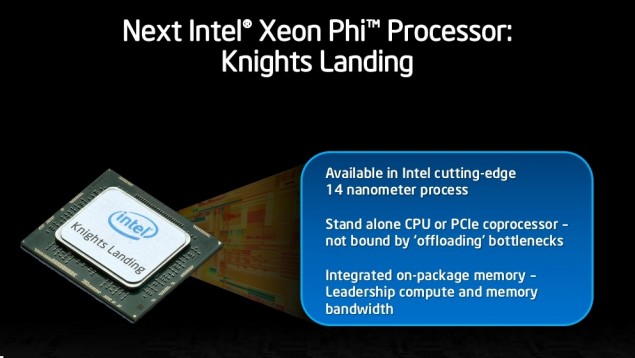

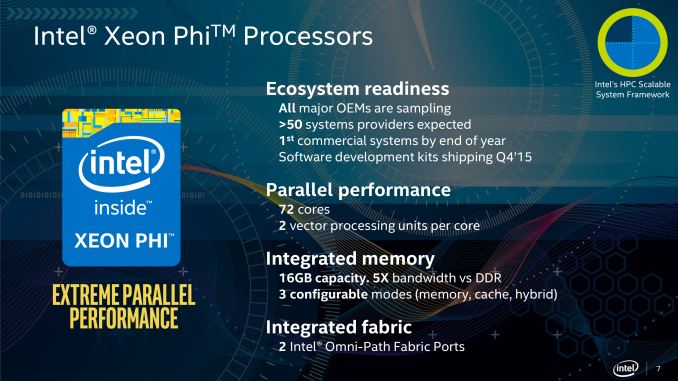

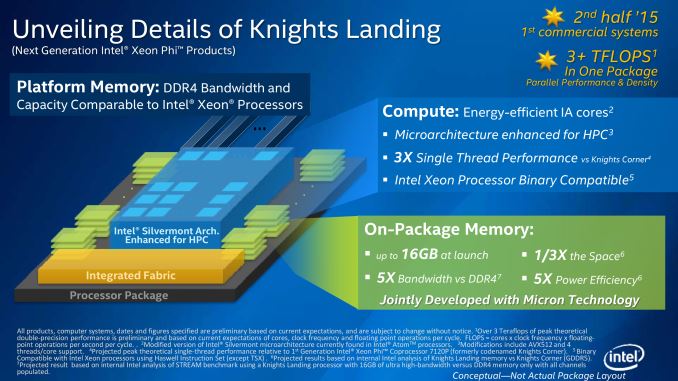

La deuxième génération est sur le point darriver, elle devrait être commercialisée cette année. Connue sous le nom de code Knights Landing, cette nouvelle mouture tient du superlatif pour ses caractéristiques : pas moins de septante-deux curs, chacun hébergeant deux unités de traitement vectoriel AVX-512 (qui travaillent sur des registres de cinq cent douze bits) ; individuellement, ces curs devraient être trois fois plus rapides que précédemment. La puce elle-même est gravée avec un processus à quatorze nanomètres, ce qui se fait de mieux pour le moment, avec notamment de grands gains en termes de puissance consommée (et de chaleur dissipée).

Larchitecture prévoit aussi des bus DDR4 pour la mémoire principale, mais surtout seize gigaoctets de mémoire intégrée sur la puce elle-même (avec une bande-passante jusquà cinq fois supérieure à celle de la DDR4, quinze fois par rapport à la DDR3, encore majoritaire dans les ordinateurs actuels). Cette mémoire sera à peu près aussi rapide que les caches L3 des processeurs actuels (bien quils soient limités à quelques mégaoctets !), avec une bande passante de cinq cents gigaoctets par seconde.

Cette super-mémoire cache utilisera linterface HMC (hybrid memory cube), concurrente de HBM (high bandwidth memory) en cours de déploiement sur les processeurs graphiques (les cartes Fury remettent AMD à lavant-plan en termes de performance). In fine, un tel processeur pourra proposer une puissance de calcul de lordre de trois téraflops, cest-à-dire trois mille milliards dopérations en virgule flottante par seconde.

Une autre nouveauté par rapport à la génération précédente est que ces coprocesseurs pourront servir de processeurs principaux et faire fonctionner le système dexploitation de la machine. Lintérêt majeur est de se débarrasser dune connexion par bus PCI-Express, qui limitait la performance de son prédécesseur (une constatation partagée par le concurrent NVIDIA, qui sapprête à proposer sa technologie NVLink).

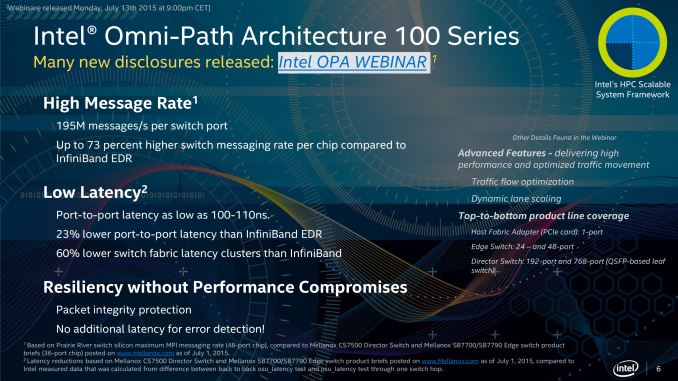

Au niveau de la communication, Intel sapprête également à communiquer plus dinformations sur son Omni Path, une interface dinterconnexion entre nuds dans un supercalculateur. Intel sapprête ainsi à marcher sur les platebandes de géants comme InfiniBand, avec une technologie présentée comme supérieure. Notamment, les latences de communication devraient être de lordre de cent nanosecondes, quand InfiniBand monte à presque deux microsecondes, Ethernet à dix à cent microsecondes.

Chaque processeur Xeon Phi Knights Landing aura deux ports Omni Path. Lobjectif semble être lintégration verticale dans les supercalculateurs, Intel ayant annoncé un partenariat avec HP pour la construction de serveurs autour des technologies HPC dIntel, rassemblées sous le nom de SSF (scalable system framework), dans le contexte de la gamme Apollo de HP.

Sources et crédit images : Intels Xeon Phi 14nm Knights Landing Co-Processors Detailed OmniPath Architecture 100 Series and 16GB HMC on a 2.5D Interposer et Quick Note: Intel Knights Landing Xeon Phi & Omni-Path 100 @ ISC 2015.

Cette entrée a été publiée dans HPC le16 juillet 2015par dourouc05.

Vous avez lu gratuitement 1 503 articles depuis plus d'un an.

Soutenez le club developpez.com en souscrivant un abonnement pour que nous puissions continuer à vous proposer des publications.

Soutenez le club developpez.com en souscrivant un abonnement pour que nous puissions continuer à vous proposer des publications.